Eliyan is transforming the

semiconductor industry.

Eliyan’s NuLink™ PHY technology enables the performance on standard packaging that others can only deliver using advanced packaging.

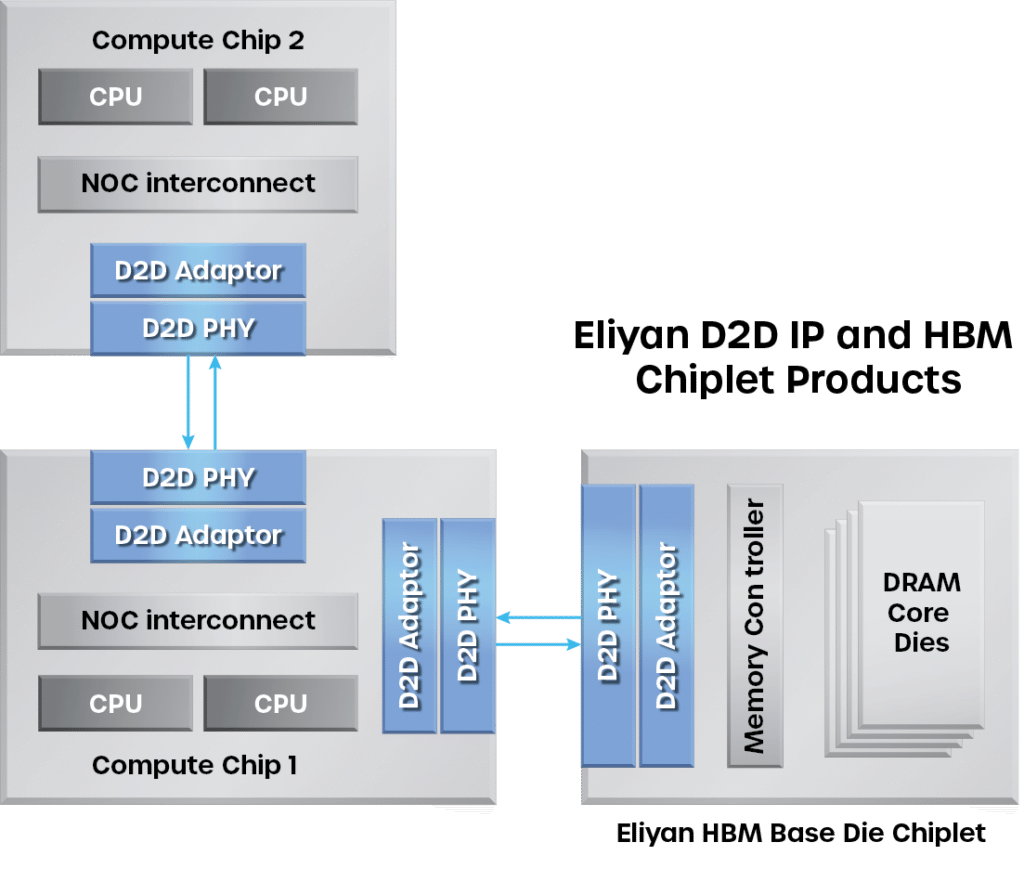

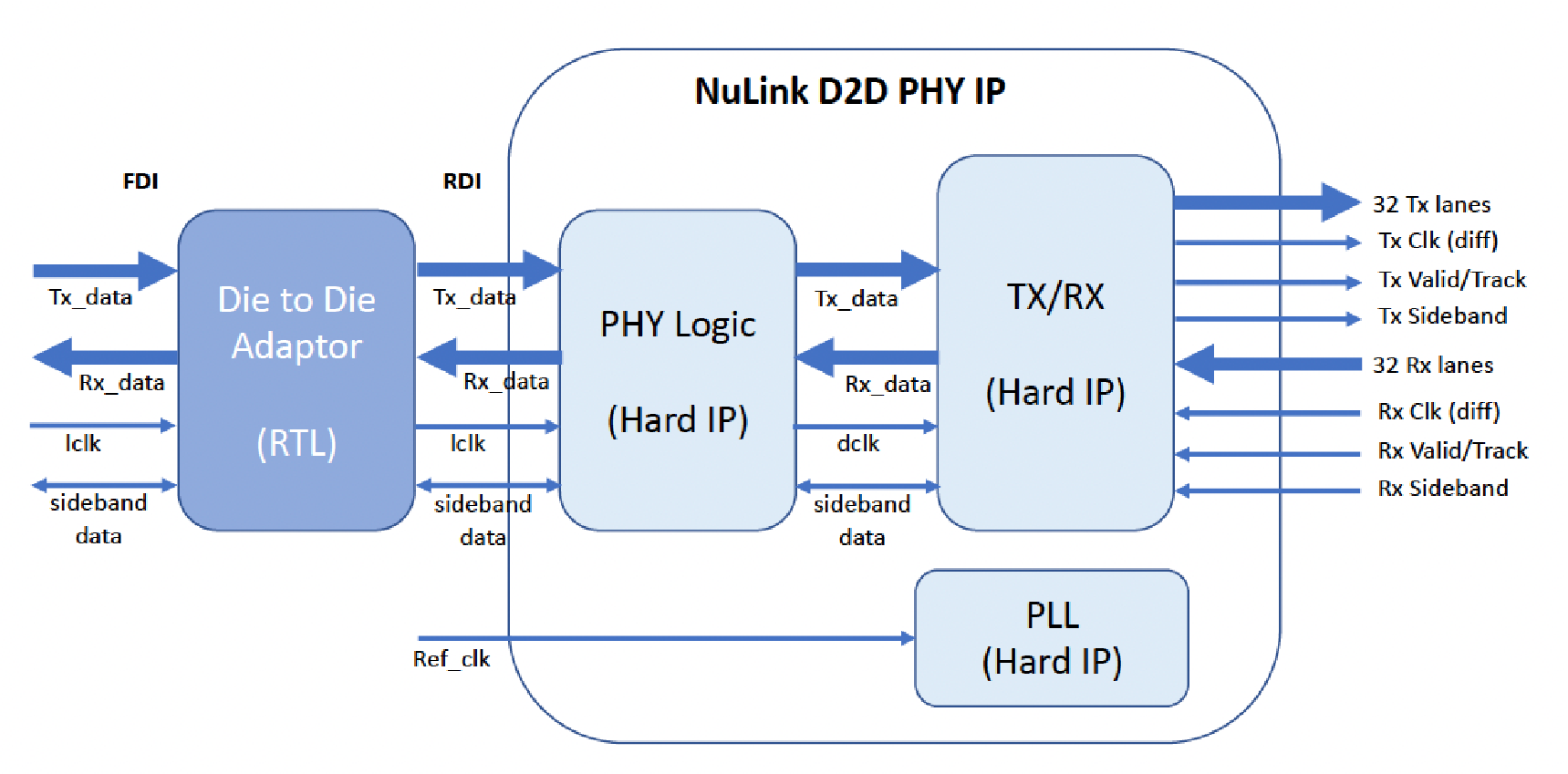

NuLink is the building block for Eliyan’s products including die-to-die PHY IP cores, die-to-memory PHY IP cores, and Chiplet products that help enable a broad range of semiconductor solutions.

NuLink™ for Die-to-Die (D2D)

PHY IP Products

UMI™ for Die-to-Memory (D2M)

PHY IP Products

Unlike fixed unidirectional die-to-die solutions, NuLink technology is able to deliver low-power and high-performance D2M solutions.

NuGear™ Chiplet Products

Eliyan Die-to-Die PHY IP Products

Eliyan uses its NuLink technology to develop die-to-die PHY IP products to support multiple standards (including UCIe and BoW) and multiple packaging types (including advanced packaging and standard packaging).

For Standard Packaging, Eliyan has a family of high-bandwidth interface IP cores that are designed to be integrated into ASIC designs to connect two dies (chiplets) on the same standard organic/laminate package substrate. Eliyan’s PHY technologies with patented implementation techniques enable the same levels of performance and power as those provided by advanced packaging options, while providing benefits to system design, cost, thermal, test, yield, and production cycle-time by utilizing industry standard packaging. In many applications this eliminates the need for advanced packaging technologies such as silicon interposers or silicon bridges.

Target Applications

- Chiplets connected on standard organic packages without large silicon interposers or silicon bridges but with interposer-like bandwidth/power/latency.

- SiP applications that benefit from up to at least four times the substrate area compared to the largest silicon interposer and thus a far higher number of chiplets in the package, resulting in major performance and power advantages.

- ASIC designs where a Network on Chip is split across two or more chiplets.

- Applications that benefit from placement flexibility to mix and match chiplets of different dimensions.

- Chiplet applications–such as HBM—where there must be physical separation between a hot ASIC and heat-sensitive dies.

Standard Package PHY Products

and Key Bandwidth Metrics

The NuLink D2D PHY IP cores for standard packaging are designed for standard organic/laminate packages with bump pitches from 100um to 130um. Eliyan has NuLink D2D PHY IP products for industry standards (including UCIe and BoW) as well as unique value-added products including UMI and SBD. The NuLink PHY IP cores typically have 64 data lanes with configuration and bump map layout dependent on the PHY type (UCIe, BoW, UMI, SBD). The table below lists key metrics for these NuLink PHY products at 110um bump pitch.

Standard Package PHY Products

and Key Bandwidth Metrics

The NuLink PHY IP cores for standard packaging are designed for standard organic/laminate packages with bump pitches from 100um to 130um. Eliyan has NuLink PHY IP products for industry standards (including UCIe and BoW) as well as unique value-added products including UMI™ and SBD. The NuLink PHY IP cores typically have 64 data lanes with configuration and bump map layout dependent on the PHY type (UCIe, BoW, UMI, SBD).

NuLink D2D PHY for Std Pkg @ 110um bump pitch

| NuLink UCIe Unidirectional | NuLink BoW 2.0 Configurable Bidirectional | NuLink UMI Dynamic Bidirectional | NuLink SBD Simultaneous Bidirectional | |

|---|---|---|---|---|

| Process Node | 5nm & 3nm | 5nm & 3nm | 5nm & 3nm | 5nm & 3nm |

| # Data Lanes | 32 Tx + 32 Rx | 64 Tx/Rx | 64 Tx/Rx | 64 (Tx + Rx) |

| Data Rate / Lane | 32G | 32G | 32G | 64G (2×32) |

| Power Efficiency | < 0.5 | < 0.5 | < 0.5 | < 0.5 |

| Beachfront BW metric | 1.8 | 1.9 | 2.1 | 2.6 |

- UCIe PHY size based on the UCIe specification.

- BoW PHY size from the BoW specification, including optional AUX signals.

- UMI™ = Universal Memory Interface utilizing dynamic half-duplex bidirectional signaling.

- SBD = Simultaneous Bidirectional signaling, with both Tx and Rx simultaneously on each wire.